US $430

Directions

Similar products from Other Semiconductors & Active Components

Linear Technology LTC4071EDDB DC1702A LI-ION Polymer Shunt Battery Charger Low

Reel of PCB Components MFG No: CRCW1206 Qty on Reel: 2000

Reel of PCB Components MFG No: CC0603KRX5R6BB105 Qty on Reel: 3200

AJAX TOCCO UK INVERTER SEMICONDUCTOR 9FP47 0626

Sunkee 10pcs Bridge Rectifier KBP307 KBP-307 SEP 3A

L-COM UJ5T568S Modular Coupler, CAT 5E RJ45 8x8 Shield

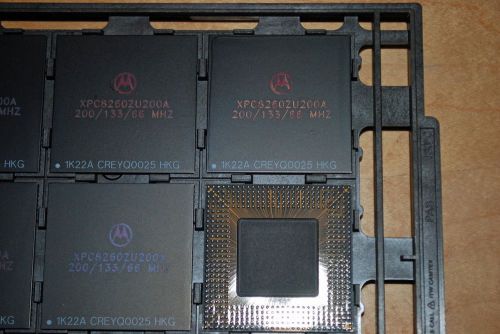

QTY 39 Motorola XPC8260ZU133A PowerQUICC II Integrated Communications Processor

QTY 21 Motorola XPC8260ZU200A PowerQUICC™ II Integrated Communications Processor

QTY 53 Motorola XPC8260ZU200A PowerQUICC™ II Integrated Communications Processor

Hitachi Semiconductor HD63484CP98 Advanced CRT Controller (ACRTC)

Reel of PCB Components MFG No: RC0603FR-0724K9L Qty on Reel: 4400

Reel of PCB Components MFG No: RC0603FR-0712K1L Qty on Reel: 4400

Reel of PCB Components MFG No: RC0603JR-072R70L Qty on Reel: 4300

Reel of PCB Components MFG No: RC0603FR-0724K9L Qty on Reel: 3900

Reel of PCB Components MFG No: RC0603FR-0724K9L Qty on Reel: 4600

Reel of PCB Components MFG No: RC0603FR-073K65L Qty on Reel: 4700

Reel of PCB Components MFG No: RC0603FR-0724K9L Qty on Reel: 4200

Reel of PCB Components MFG No: RC0603FR-0712K1L Qty on Reel: 4300

GRACE P-M8R2-M3R3 GRACEPORT INTERFACE ***NNB***

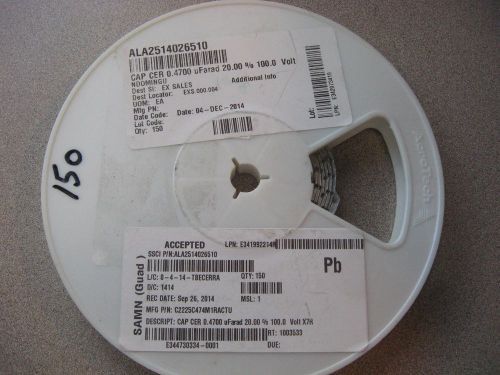

Reel of PCB Components MFG No: C2225C474M1RACTU Qty on Reel: 150

People who viewed this item also vieved

Maxim MAX3162CAI+ 1µA, RS-232/RS-485/422 Multiprotocol Transceivers MAX3162

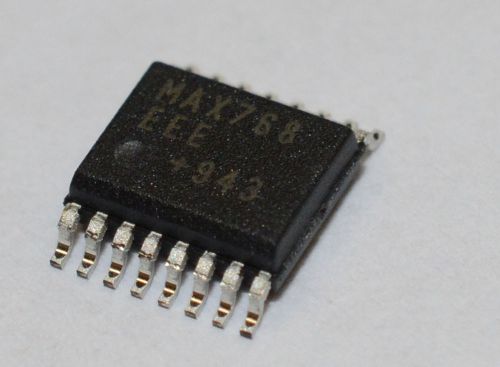

Maxim MAX768EEE+ Low-Noise, Dual-Output, Regulated Charge Pump MAX768

Moeller Buzzer M22-XAM ( M22XAM ) NIB , QTY 10 Per Lot !

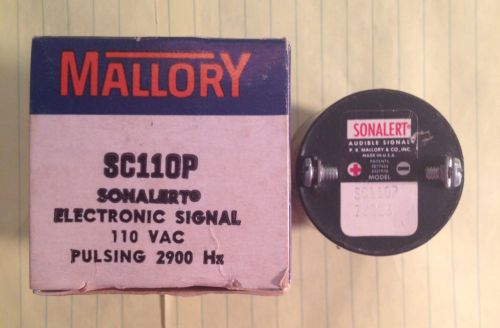

MALLORY - SONALERT - SC110P - 110VAC - PULSING 2900HZ - ELECTRONIC SIGNAL

Werma Buzzer 64580975 Surplus Product, New !

STMICROELECTRONICS ESDA6V1U1RL TVS DIODE ARRAY, 200W, 6.1V, SOIC (1000 pieces)

ON SEMICONDUCTOR MBRB1045T4G SCHOTTKY RECTIFIER, 10A, 45V, D2PAK (1000 pieces)

6.2 inch KR062PA2S AS HSD062IDW1 800*480 60Pin LCD Display Screen For Car-DVD

EL Lamp Driver IC P/N: IMP803 (lot of 5)

ACX709AKN Sony 320x320 TFT Color LCD with Touch Screen

8.4" inch AUO G084SN05 V.7 v7 800*600 LCD Display Screen Panel MobileDemand

SA40A TRANSIENT VOLTAGE SUPPRESSOR ** NEW ** ( 10 PCS )

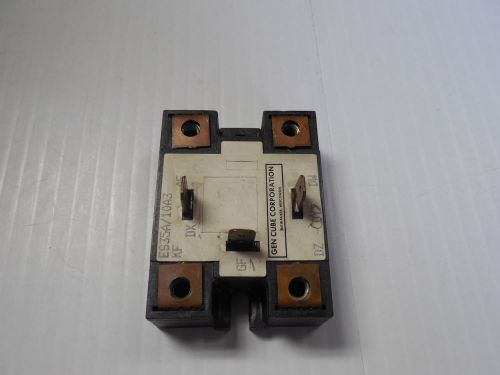

GEN CUBE CORPORATION POWERTHERM MODULE 104X125DC12ST ES35A/10A3

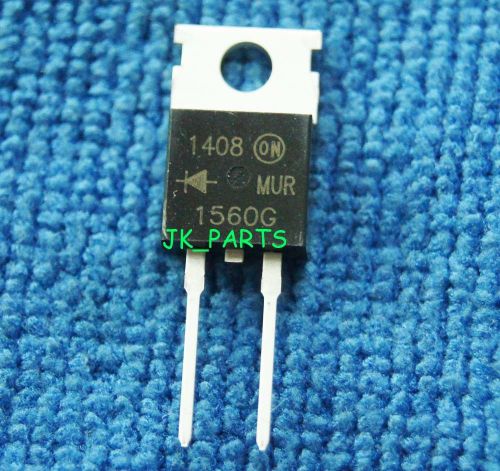

50pcs New MUR1560G MUR1560 15A 600V UltraFast Rectifier Diode TO-220

NMB-Mat Fan for Home Theatre systems.

PRX T9G0161003581011 RECTIFIER POWER MODULE THYRISTOR CONTROL D204936

PRX T9G0211003 58 1213 RECTIFIER POWER MODULE THYRISTOR CONTROL D204933

SIEMENS 6SN1145-1BA01-0DA1 power supply 90 days warranty

By clicking "Accept All Cookies", you agree to the storing of cookies on your device to enhance site navigation, analyze site usage, and assist in our marketing efforts.

Accept All Cookies