US $430

Directions

Similar products from Other Semiconductors & Active Components

Reel of PCB Components MFG No: RC0402FR-07510R Qty on Reel: 5000

Reel of PCB Components MFG No: RC0402FR-07510K Qty on Reel: 7900

Reel of PCB Components MFG No: RC0603FR-751RL1 Qty on Reel: 3900

Reel of PCB Components MFG No: RC0603FR-07121RL Qty on Reel: 1700

Reel of PCB Components MFG No: C0603C223K5RAC7867 Qty on Reel: 3900

Reel of PCB Components MFG No: RK73B2BTTD2R7J Qty on Reel: 4600

Reel of PCB Components MFG No: CC0603KRX7R7BB274 Qty on Reel: 1100

Reel of PCB Components MFG No: ERJ14NF10011U Qty on Reel: 5000

Reel of PCB Components MFG No: RC0603FR-0751R1 Qty on Reel: 2600

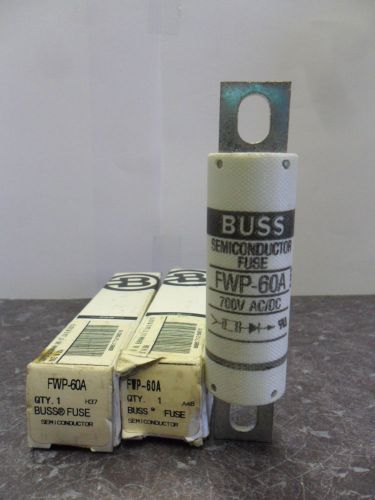

New Lot Bussmann 700V Semiconductor Fuses FWP-60A Shawmut A70P60 L70S60NIB

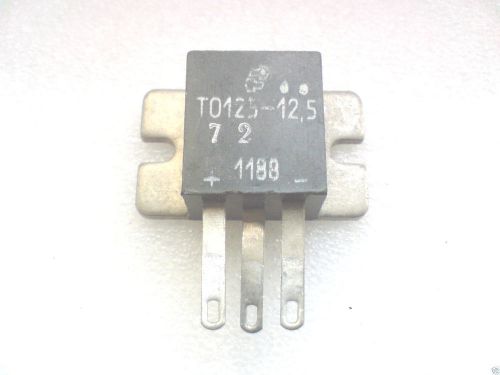

Thyristor Opto TO125-12,5 12,5A 1000V USSR

NEW, SET OF 9 NTE53 NPN SI HV Speed Switch TO-3. FREE SHIPPING

Dark Gray Toroidal Core Transformer Power Inductor Ferrite Ring 45mmx26mmx15mm

Scitex NuBus Card, XC96002RC40 DSP, SRAM daughterboard

108 x SMD IC ACTEL , A40MX02-PL44I , FPGA , (PLCC44)

36 x VECTRON INTERNATIONAL CO-233/233Y1417-80MHZ XTAL OSCILLATOR 80MHz CO-233

840 x IC FREESCALE SEMICONDUCTOR MC145502P PCM Codec-Filter Mono-Circuit , 22DIP

Semikron SKM75GB176D Semitrans M IGBT Power Module Semikron IGBT *Fully Tested*

FUJI IGBT MODULE 6MBP75RA060-02 1200V/75A

People who viewed this item also vieved

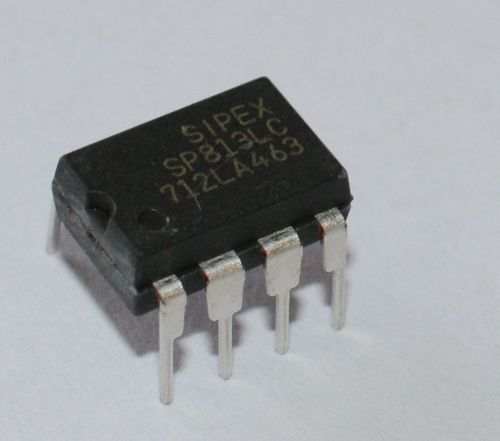

Exar SP813LCP-L Low Power Microprocessor Supervisory Circuits SP813

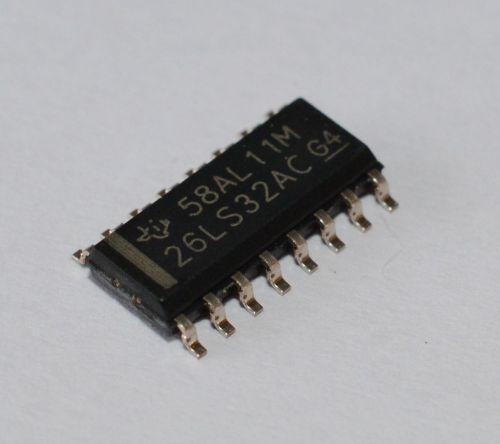

10x TEXAS INSTRUMENTS AM26LS32ACD DIFFERENTIAL LINE RECEIVER 26LS32

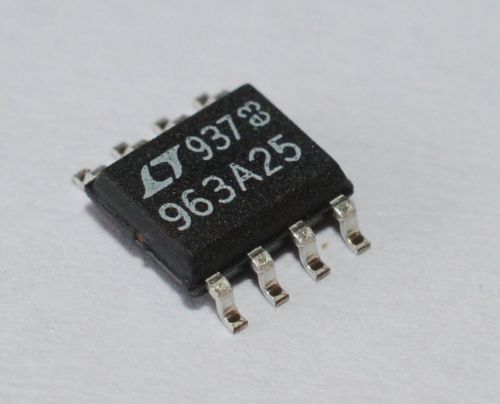

Linear LT1963AES8-2.5 1.5A Fast Transient Response LDO Regulator LT1963 963A25

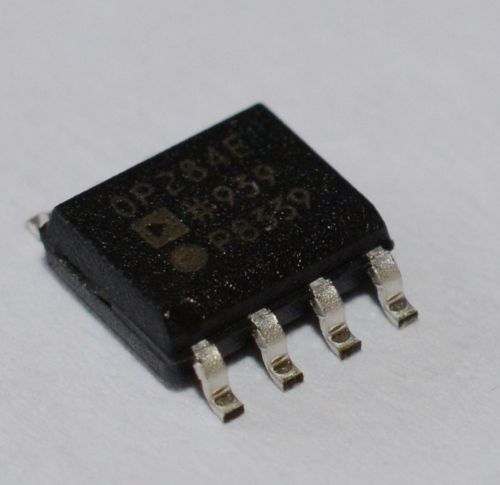

Analog Devices OP284ESZ Input and Output Operational Amplifiers OP284

LOT OF 5 62808-001 DOUGLAS RANDALL Audio Buzzer

LOT of 5 212-0169 AUDIO BUZZER PCB Mount Radial Leads

ALLEN-BRADLEY 855H-BCD24ADR6 SIGNALING DEVICE - NEW!

Star CMB 12 Buzzer New Old Stock

16 x 1A 10kV 100ns High Voltage Diode HV Rectifier HF Tesla Coil Ham Radio

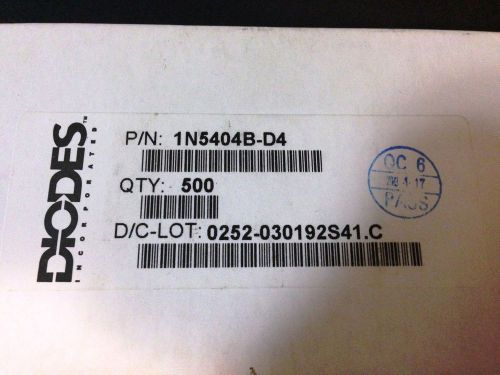

DIODES INC.1N5404B-D4 RECTIFIER STANDARD RECOVERY O/J DO201 (NEW-800 PIECES)

AA112 Gold Bonded Diode lot of 5 pieces

100 x 1n4001 Fairchild Rectifier Diode

NS12-TS00-ECV2 12.1" HMI Touch Glass Panel Original New

original High voltage circuit board for Touch Screen HMI XBTGT6330

New Original Touch Glass Used on 12.1" HMI Touch Screen NS12-TS01B-V2

LCD Panel KG057QV1CA-G000 For 5.7" HMI NT31-ST122B-EV2 Original New

Vintage AEG full wave Selenium Rectifier 20V / 0.5A Tested!

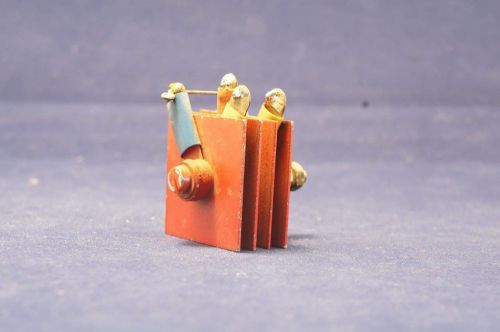

Phenolic Switch Wafer for rotary switch, single pole - 11 positions - NEW!!

Pair of Vintage AEG / Grundig Selenium Rectifier 30x30x120mm 230V / 350mA

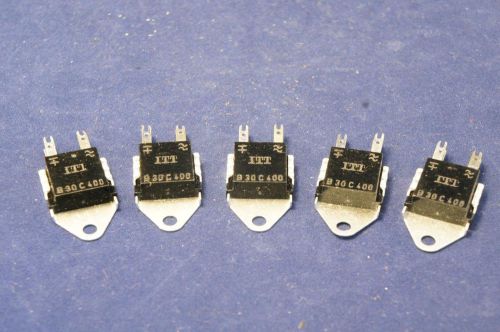

NOS Vintage ITT Rectifier - full wave - 30V / 400mA - Tested!

5PCS X NTB30N20T4G 30A/200V TO-263 FET Transistors(Support bulk orders)

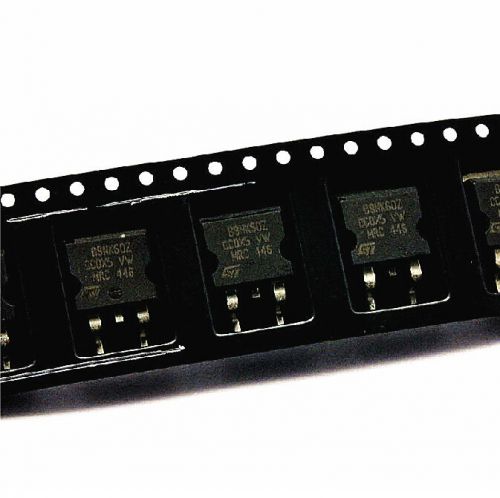

5PCS X STB9NK60ZDT4 7A/600V/125W TO-263 FET Transistors(Support bulk orders)

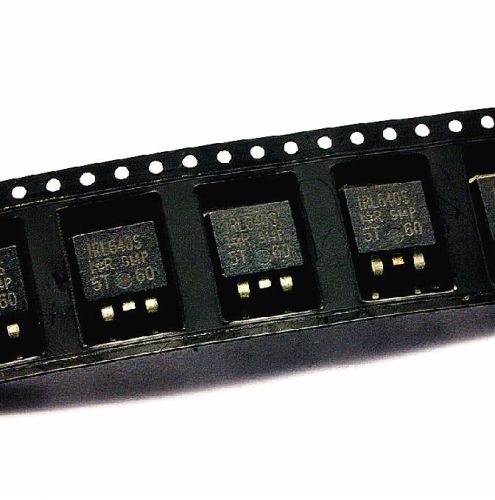

5PCS X IRL640S 17A/200V/125W TO-263 FET Transistors(Support bulk orders)

SOLITRON 3N188 METAL CAN IC PULLED FROM WORKING TEST EQUIPMENT

By clicking "Accept All Cookies", you agree to the storing of cookies on your device to enhance site navigation, analyze site usage, and assist in our marketing efforts.

Accept All Cookies